我们提到芯片工艺时,都会说它是7nm、5nm、3nm等工艺的,数字越小,代表越先进,技术难度越大。

那么大家知道这个5nm、3nm到底指的是芯片中的哪一个元件的尺寸为5nm、3nm么?

其实在100nm之前,这个XX纳米,对应的芯片工艺中,栅极的宽度,也就是漏极到源极的宽度,它是多纳米,芯片就是多少纳米工艺的。

但喜欢钻空子的芯片厂们,就开始钻窗子了,既然栅极宽度,代表工艺,那么就想方设法缩短它,不就工艺提升了么?

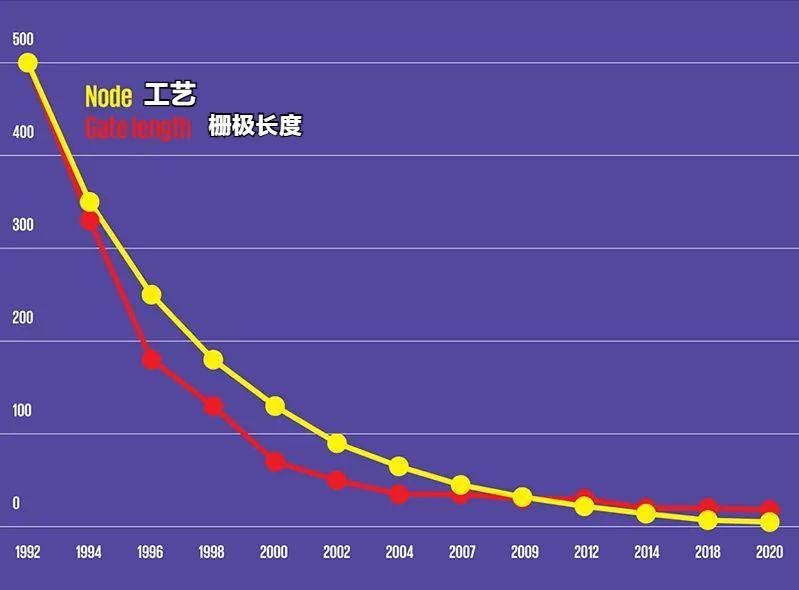

于是从100nm开始,一直到2007年的40nm左右,这10多年的时间里,出现了一个倒挂,那就是芯片工艺实际上是落后于栅极宽度的。

如下图所示,可以很明显的看到,之前是Node(工艺)和Gate length(栅极长度)是对应的,后来工艺后来了。

再到40nm以下时,栅极宽度,又大于芯片工艺了,因为栅极宽度,无法持续缩小,一旦太小了,会不稳定,有各种场效应。

后来,业界提出了另外一个参数,也就是金属间距(metal Pitch)的一半来代替这个栅极宽度,但这个影响到了各晶圆厂们“吹牛”,大家不接受,也不对外公开这个数值。

所以,目前芯片制造厂们的芯片工艺,其实是不公开透明的,都是用等效工艺来说。

不过,如果去较真,还是可以用金属间距(metal Pitch)的一半来看看其具体工艺如何的。

而近日,ASML认为,摩尔定律没死,还在持续前进,到2039提时,甚至会达到0.2nm,但这个只是说法而已,实际工艺应该是多少呢?ASML也做出了一一对应。

如上图所示。ASML将芯片工艺(Node name)、metal Pitch(金属间距)进行了一一对应,而将metal Pitch除以2,就是半金属间距了。

可以看到,在5nm时,实际金属半间距是14nm左右,而3nm时,则是11.5nm,2nm时是11nm左右。1nm时,是9nm,到Sub-0.2(升级版0.2nm)时,这个半金属间距,实际上是6nm。

这个其实代表的才是芯片实际真实的工艺水平,这个金属半间距的进步和提升,是远远落后于芯片工艺,但晶圆厂们,不会告诉你听的。

京公网安备 11011402013531号

京公网安备 11011402013531号